6. BJT

; Junction이 2개있는 반도체 소자(pnp, npn이 있음)

- 동작 조합 (eb, cb의 bias 조합의 따라 4가지가 가능)

a. active

; GAIN,신호증폭, 앰프구현에 사용

; 첫 np를 수평으로 맞추고 마지막 n의 경사를 키운다.

; drift(major carrier) -> diffusion(minor) -> E-field(major) 로 carrier 이동

b. saturation

; Switch 구현에 사용

c. cutoff

; off - state(동작 안함)

d. inversion; 안씀

7. MOSFET

; FET는 제어단자에 따라 이름 붙인다(JFET,MESFET...)

; 그 중 MOSFET는 제어단자가 단자부터 보면 METAL - SiO2 - Si 로 이루어져 MOSFET 이다.

사진 설명을 입력하세요.

- 제작 할 때, 채널 생성 여부에 따라 enhanced, depletion으로 분류된다.

- 보통 enhancement로 만든다

- enhancement ; 채널 있음, default off

- depletion ; 채널 없음, default on

- MOSFET의 제 1 원칙 ; 채널로만 전류가 흐르는 소자.

- MOSFET은 기판을 쓴다. 근데, 기판이 넓어서 이쪽으로 누설될 우려가 있다.

- 이것을 막기 위해, n-well과 p-sub 사이는 항상 reverse bias를 걸어, 전류가 못흐르게 함.

- reverse bias ; ( p 전압(0 or -) << n 전압 (+) )

- 채널형성

; gate에 (+) 전압을 걸어본다.

; 그러면 산화막 아래도 (+)로 대전될 것이고, 그 밑에는 (-), 즉 전자가 모인다.

; n형 채널이 되고, 이 채널을 inversion layer(반전층) 이라 한다.

; 기판이 p-sub이라 n - channel을 inversion layer라 한다.

; 이, 채널을 만들기 위한 전압을 MOSFET에서 threshold-voltage(문턱전압)라 한다.

; n 채널은 p기판이라, (+)를 가하므로

- 전류 도통

; 채널 형성 이후 source - drain 에 전위차를 만들어 주면 전류가 흐른다.

; drain에 (+) source에 GND(0V)를 건다.

전류는 channel size로 하므로 Vgs가 담당한다.(게이트 전압)

- 상태구분

; 차단상태

; 채널이 없는 상태이다.

; 따라서 Vgs(게이트전압, source는 0V다) < Vth다.

; 비포화 상태(non-saturation or triode)

; 채널이 형성됐다. 그러나 아직 drain에 전압을 걸지 않았다. (Vds < Vgs-Vth)

; Vgs-Vth 는 채널이 형성되었다는 뜻.

; Vds는 drain에 아직 적절한 전압이 안걸렸다는 뜻.

; 평평한 채널이 된다.

;BJT의 saturation과 같다.

;즉, switch로 사용된다.

;포화상태(saturation)

; drain에 채널보다 큰 전압이 걸렸다. (Vds > Vgs-Vth)

; 삼각형 채널이 된다.(drain(+된) 쪽이 얇은)

; drain부근에서는 강한 전계에 의해 전자가 빠르게 drain으로 끌려감

; 따라서, drain전압은 drain전류 변화에 영향을 주지 못함.

; 포화의 의미는 Vds가 커진다 해도 Id는 일정해짐 에서 나왔다.

; 어쨋든, 전류에 Vds 영향이 사라진다.

; BJT의 active와 같다.

; 즉, AMP로 사용된다.

; 위에서 삼각형 채널 상태를, pinch-off라 한다.

cf)핀치오프(pinch-off) ; gate전압의 수직전계와 drain전압의 수평전계가 서로 상쇄되어 drain근처에서 채널이 형성되지 못하는 상태.

- 각영역에서 전압 관계와 전류 수식(전류만 보자 전압은 위의 원리 이해했으면 같은 거니까)

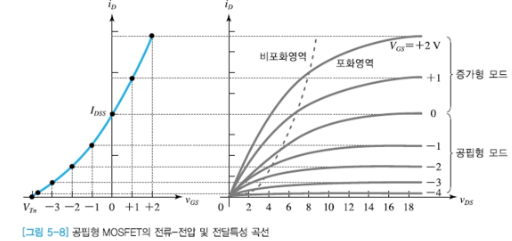

- MOSFET IV curve( id - Vds, 드레인에서 전류 전압 그래프)

- 여러 효과들

;channel length modulation(Vds때문!)

; drain전압이 너무 커지면, pinch - off가 증가하여 drain 쪽 채널이 점점 사라져 버리는 현상.(유효 채널 감소)

;Vds에 따라 Id가 변하는 현상

; 아래 식에서 1+ λ 부분이다

; λ : 채널길이 변조계수

; MOSFET이 작아지면서, ΔL /L이 커져 효과도 커짐.

; 아래 그래프에서 위로 뜨는 부분.

; BJT에서는 early effect와 같다.

- 여러 효과 중 short channel effect관련

; 실 제작 시 너무 작아져서 생기는 현상!

;채널길이가 1um 이하에서 발생하는 여러 second effect들의 총칭

; 수평,수직 전계가 증가하여 기존에 무시했던 parameter 들이 영향을 미친다.

;이 부분은 너무 많아서 따로 분류한다.

; DIBL : drain전압이 ro를 낮추는 효과

;surface scattering

;velocity saturation

;impact ionization

;Hot carrier injection

;punch-through

- MOSFET 성능판단

; output characteristic : Saturation current(On-state 특성)

;Transfer characteristic

Threshold voltage(On/Off switching speed)

Subthreshold leakage(Off-state 특성)

8. MEMORY ( DRAM / FLASH)

- 캐패시터 에너지 저장 원리

; 근본 원리는 전기장의 형태로 바꿔 저장한다.

; 극과 반대 전하가 극에 모이는 형태

; C= εA/d(면적이 넓으면 많이담고, 판사이 인력이 강하면 많이 담는다.)

; C = Q/ΔV 이다. V가 줄면 C가 늘어난다. 그래서 d를 줄이고 유전체를 넣어 V가 주는 모양을 만드는 것이다. V가 주는 효과가 일어나면 그만큼 채우기 위해 전하량이 늘어난다.(양 연결 전압만큼 만들어져야 하므로)

- 유전체의 효과

; 유전체에 전기장을 가하면, 분극, 정렬을 통해 상쇄하는 전기장을 만든다.

; 외부에서는 전기장이 약해진 것 처럼 보인다.

; 그러내 내부 전계는 강해지는 것이다.

- DRAM

https://www.rohm.co.kr/electronics-basics/memory/memory_what2

https://blog.naver.com/cj3024/221418877536

https://m.blog.naver.com/narabaljeon/220718012527

https://blog.naver.com/genie6930/221283465082

'전공지식정리 > 반도체' 카테고리의 다른 글

| 반도체 테스트(WT & PKT& ESD..) (0) | 2022.01.20 |

|---|---|

| 반도체 정리 - 테스트용 키워드 (0) | 2022.01.20 |

| 반도체 정리(1~5) (0) | 2022.01.20 |

| 소자 공부 2 (0) | 2022.01.20 |

| 소자공부 1 반도체 소자의 종류 (0) | 2022.01.20 |