- 해석한게 많아서, 영어를 병기합니다. 이상한 말 있으면 알려주세요 -

단순 개념 설명은

https://blog.naver.com/jh_h1022/221265629048

HDL(VHDL,Verilog)

1. HDL은 2가지가 있다. IEEE(아이 트리플 E라고 읽는다)의 인증을 받은 것 2가지 1. VHDL 2. ...

blog.naver.com

여기에 있습니당

1. 디자인 Tool의 변천 (pencil & ruler)

1. 연필과 자

; 연필과 자를 이용해서 직접 회로를 그렸다.

=> 2. 회로도 편집기(schematic editor)

; 손으로 그리던 것을 컴퓨터를 이용해서 그릴 수 있게 되었다.

=> 3. 하드웨어 표현 언어 (HDL)

; 언어로 coding을 하면, 컴퓨터가 알아서 그리도록 발전하였다.

Evolution of design tools

(pencil & ruler) => (schematic editor) => HDL

schematic n.회로도 adj. 도식적인, 도식의

editor n. 편집기

Digital Design tool의 변천(시간순서는 좌에서 우로)

1.1 HDL(hardware description language)

;하드웨어 표현 언어

- 1세대(1st generation) : PALASM, CUPL, ABEL

- 80's 중반 : VHDL, verilog HDL

1.2 VHDL, verilog

; HDL의 대표적인 언어로써, 두 언어는 아래의 기능을 제공한다

1.2.1 모듈적이고, 계층적인 coding(modular and hierarchical coding)

; hierarchy란 말은, 계층적이란 뜻으로, 층을 나눠서 설계한다는 뜻이다.

=> 모듈, hierachy방식은 큰 규모의 시스템 설계를 쉽게해준다.

ex) 1번째 신호처리 ->(연결) -> 2번째 신호처리

이런식으로 단을 나눠서 연결하는 것이다.

밑의 5.2에 그림이 있으니 이해가 안가면 그림을 참고하길 바람.

1.2.2 rich variety of high - level constructs

=> ex)arrays, function calls

1.2.3 시작은 시뮬레이션 언어다.

; 회로 합성 기능은 나중에 추가되었다.

synthesis n. 합성

은 언어를 토대로 회로를 합성해 주는 것이다.

simulation은 단순 입출력, 혹은 코드가 잘 돌아가는 지 보는 것으로 둘은 차이가 있다.

VHDL, verilog

modular and hierarchical coding

=> ease the design of Large - scale system

rich variety of high - level constructs

=> ex)arrays, function calls

started as simulation language

=> synthesis features added later on)

2. HDL을 쓰는 이유.

2.1 직접 그리는 것의 어려움.

그림으로 표현하는 것은 VLSI, ASIC에 적절하지 않았다.

; VLSI, ASIC 처럼 회로의 미세함, 복잡성이 올라갈 수 록

사람이 그리는 것이 어려워진다.

(schematic tool도 사람이 그리는 것이다.)

2.2 추상화의 수준이 올라감

=> 더 복잡하고 큰 규모의 디자인이 가능해진다.

ex) assembly -> C/C++, JAVA (어셈블리가 C/JAVA로 발전했듯이)

; ex) multiplexer회로 => MUX라는 단어로 표현 끝.

2.3 compiler/ synthesize가 똑똑해졌다.

; 자동 회로 합성도 충분히 performance 최적화가 가능해 졌다.

2.1 graphical representation does not fit well to VLSI, ASIC

2.2 level of abstration raised

can design more complex and larger

2.3 there's sacrifice in performance.

(compare with hand-optimized)

==> so, compiler/synthesizer becomes smarter.

==> don't care!

3. HDL tool suites(묶음)

suite : n. 관련프로그램들의 묶음

3.1 기본구성

-> Text editor, Compiler, Synthesizer, Simulator

; (text editor => compiler => simulater)+ synthesizer

3.2 추가구성

+) Template generator, Schematic viewer, translator, Timing Analyzer, Back annotator

4. HDL로 design할 때의 flow

HDL - based design flow

이 과목에서는 front-end 부분에 비중을 많이 둔다.

front : block diagram -> coding -> compile -> simulation

back : synthesis -> place/route(P&R) -> timing

5. VHDL

- IEEE의 지원을 받았다.

- 1987, 1993, 2002년에 IEEE에 의해 표준이 정해짐.

5.1 특징

- 계층적 설계

- 인터페이스 좋음

- 정밀하게 기능 design 가능

- behavioral, structural하게 design 가능

- 동시동작, 타이밍, 시간에 관한 것도 모델링 가능

- 논리동작, 타이밍 시뮬레이션 가능

- hierachical design

- well-defined interface and precise functional specification

- behavioral and structural specification

- concurrency, timing, and clocking can be modeled

- logical operation & timing behavior can simulate

5.2

VHDL의 프로그램 구조(Program structure)

; 여기부터 중요한 부분이니까 제대로 집중해야한다.

5.2.1

인터페이스와 동작 부분을 분리

Seperation btw interface and implementation

=> entity 부분과 architecture 부분

=> entity 선언은 Wrapper로서 기능한다.

=> entity 안에 architecture의 상세한 부분은 숨긴다.

interface = entitiy

implementation = architecture

ex) 조이스틱을 예로 들면, 우리는 키와 버튼(interface = entity)만 누르지

안에 회로의 동작(implementation = architecture)을 생각하지는 않는다.

인터페이스와 동작부분을 분리(entitiy & architecture)

5.2.2

hierachical use(계층적 사용)

in·stan·ti·ate vt. 예를 들어 설명하다.

프로그래밍에서는 다른 의미이지만, 원 의미를 아는 것이 이해에 도움이 된다.

https://terms.naver.com/entry.nhn?docId=3532994&cid=58528&categoryId=58528

5.2.3

Entity(인터페이스부분) declaration(선언)

- 바깥의 인터페이스 신호를 정의한다.

- keyword는 아래와 같다.

=> entity/is/port/end

=> 모드(mode) = in/out/buffer/inout

=> 신호종류(signal type)

- 식별자를 선언한다(entity, signal의 이름)

- Define the external interface signals

- keywords(reserved words)

- entity/is/port/end

- mode = in/out/buffer/inout

- signal type

- identifiers

: entity-name/ signal-name

entity 선언(declaration 부분)

5.2.4

architecture definition(정의)

- type/signal(내부의)/constant/function/procedure/component를 선언한다.

- begin ~ end 구문에서 동작을 서술한다(concurrent)

ex) signal 선언 방법 => signal signal-names : signal-type;

ex)예제 : 'inhibit' gate VHDL implementation

- 예제 설명

entity(인터페이스 선언)

Inhibit은 port X,Y가 BIT type으로 들어오고

port Z가 BIT type으로 나간다.

architecture(동작 선언)

Inhibit의 architecture, Inhibit_arch는

Z 는 '1'이다 ( X='1'이고 Y ='0'일 때)

이외에 Z = 0

entity에서는 inhibit의 port등을 선언하고(interface, 입출력 신호 선언)

architecture에서는 begin~end를 통해 동작을 상술한다.(implement)

VHDL은 두 부분으로 나뉘는 것을 다시한번 새겨두자.

이후의 내용은 entity와 architecture 내부의 세부적인 문법 technic이다.

5.2.5

Type

; Signal, variable, constant는 type이 있다.

=> 무조건 정해줘야 한다.

5.2.5.1

이미 정의해 놓은 type

5.2.5.2 이미 정의해놓은 연산자

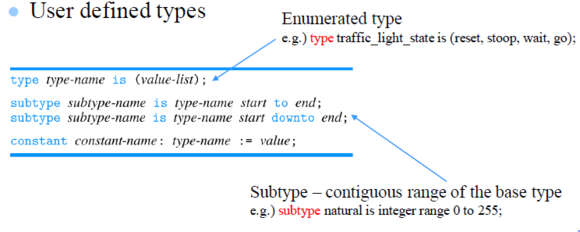

5.2.5.3 사용자 정의 Type

5.2.5.4 IEEE 1164 std_logic

; IEEE에서 정해놓은 7가지 type

=> 7가지의 가능한 type을 정의해 놓음.

-> 왜 '0', '1' 말고 U, Z,W등의 값이 있을까?

=> 왜냐하면 meta stable한 상황이 자주 발생한다.

5.2.5.5

Arrays선언 문법

위의 모든 방법 다 가능.

ex)

5.2.5.5.1

Array access(접근)

- array이름과 index로 접근한다

Accessed using the array name and index in parentheses

ex) M(11), B(5), W(WORD_LEN-5), R(1,0), R(0) ......

- 값 설정(Set values)

B := ( '1', '1', '1', '1', '1', '1', '1','1' );

B:= "11111111";

W:= (0=> '0', 8=> '0', 16 => '0', 25 = '0', others => '1')

W:= "11111110111111101111111011111110”;

- Array 자르기(Slice)

ex) B( 3 downto 0), R(1 to 2)

- Concatenation(문자열 붙이기)

; concatenate

v.사슬같이 잇다. 연쇄시키다.

ex) "011Z"

'0' & '1' & "1Z"

==> signal(신호), constant(상수), variable(변수)는

1. 이미 존재하는 type, operator로 type을 정해주거나,

2. 사용자 정의 type(IEEE 1164 std_logic, Array등)

으로 type을 정의한 뒤 정해주어야 한다.

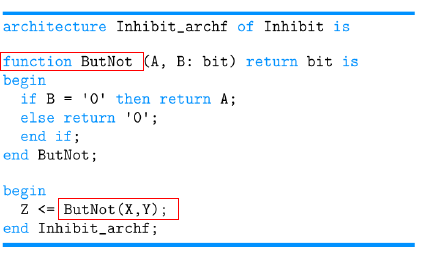

5.2.6 Function(함수)

- 몇개의 독립변수를 받아서 결과를 반환한다.

= accepts a number of arguments and returns a result

- argument n. (수학의) 독립변수. 논쟁이란 뜻도 있다. 그러나

프로그래밍에서는 독립변수의 의미로 사용한다.

- 기능을 다루는 부분이므로, 당연히 architecture부분에 선언된다.

함수의 문법 구조

ex) 위의 inhibit 예제를 함수를 추가해서 구현 함.

함수 선언 예제

- 함수 ButNot은 (A,B를 bit type 변수로 받는다) 그리고 bit type 결과를 반환한다.

- B = '0'이면 A를 반환하고 아니라면 '0' 을 반환한다.

- begin ~ end는 위에서 봤듯이 동작을 선언하는 부분이다.

=> Z 는 ButNot함수에 (X,Y)를 넣은 결과를 대입한다.

5.2.6.1 Operator Overloading

: 연산자 오버로딩

객체 지향 컴퓨터 프로그래밍에서 다형성의 특정 경우로 다른 연산자들이 함수 인자를 통해서 구현을 할 때를 말한다.

ex) add (a, multiply (b,c))

add라는 연산에 multiply라는 함수가 들어가있다.

; 연산자에 따라 그것들의 피연산자의 유형에 완전히 다른 의미를 줄 수 있기 때문에 연산자 오버로딩은 종종 비판을 받아왔다.

- IEEE 1164 std_logic 패키지는 여러가지 많은 함수를 정의해 놓았다.

=> (overloaded operator)

std logic의 table을 정의해 놓고, 이 값들을 연산자 overload에 사용한다.

위의 예제를 보면, and는 and_table(L,R)이라는 미리 정의된 함수 연산을 통해 값을 반환한다.

5.2.7 Procedure(값을 return하지 않는 함수)

; 함수랑 동작이 비슷하지만, 값을 return하지 않는다.

5.2.8 Libraries & Packages

5.2.8.1 Library

=> VHDL 컴파일러가 특정 프로젝트 정보를 저장하는 장소.

- 디자인 할때는 , 자동적으로 work라는 이름의 library를 만들고 사용한다.- file의 시작에 library 이름을 “library” clause를 이용해 지정해줘야 한다.

ex) library ieee;

clause n.절(문장 성분)

5.2.8.2 Package

; Object의 정의를 가지고 있는 파일.(다른 프로그램에서 쓸 수 있음)

ex) Signal, type, constant, function, procedure

,component declarations

- 'use'라는 구문을 이용해서 , Package를 포함시킬 수 있다.

ex) use ieee.std_logic_1164.all;library는 workspace, package는 c언어의 library같은 느낌이다.

5.3 VHDL 디자인 원칙(VHDL Design Principle)

이하는 architecture design에 관한 부분이다

(entity는 외부신호니까)

5.3.1 Architecture의 mainbody

Architecture는 concurrent한 구문의 연속이다.

concurrent ; adj. 동시에 발생하는.

c.f.) sequential statements in C, Java

=> sequential은 순차적으로 동작하는데,

vhdl의 architecture의 각 구문은 같은 타이밍에 돌아간다.

이거 들어간 다음에, 이거돌고 이런거 없다.

모든 문장이 동시에 동작한다.(병행처리)

출처

1. Digital Design: Principles and Practices, Fourth Edition, John F. Wakerly

2. KOCW. 디지털시스템설계. 아주대학교. 양회석. http://www.kocw.net/home/search/kemView.do?kemId=1145013

'전공지식정리 > 디지털시스템설계' 카테고리의 다른 글

| VHDL 코드 개념, 구조 (0) | 2020.12.08 |

|---|---|

| 4. Timing과 Simulation (0) | 2020.12.08 |

| 디자인스타일 3. Behavioral design (0) | 2020.12.08 |

| 디자인스타일2. Dataflow Design (0) | 2020.12.08 |

| 디자인 스타일 1. Structural design (0) | 2020.12.08 |